臺積先進封裝 成AI算力關鍵

圖/美聯社

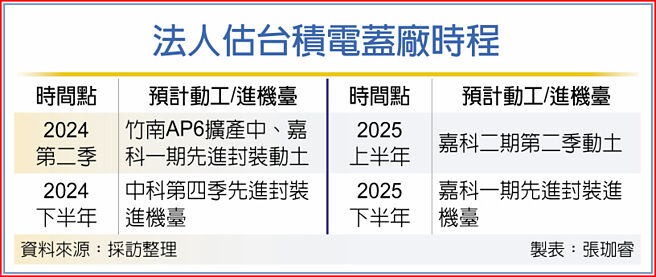

法人估臺積電蓋廠時程

AI算力需求狂飆,先進封裝產能成關鍵!法人指出,臺積電着眼先進封裝成長性,包括中科、南科、嘉科均進入擴產進行式,今年拍板的嘉義科學園區預計先行興建二座先進封裝廠,嘉科一期將於本季動土,明年下半年進機,嘉科二期預計明年第二季動土,2027年首季度進機,續擴AI、HPC市佔大餅。

有別於摩爾定律,追求半導體晶片不斷微縮,先進封裝技術透過堆疊,提升輸入/輸出的密度,從而提高晶片性能。臺積電近期揭示衆多次世代先進封裝,涉及多個新技術和工藝,包括CoWoS-R、SoW等。先進封裝技術的發展對於晶片產業進步具有重要意義,臺積電創新解決方案帶來革命性的晶圓級效能優勢,滿足超大規模資料中心未來對AI的要求。

半導體業者表示,臺積電推出系統級晶圓技術,使12吋晶圓能夠容納大量的晶粒,提供更多運算能力,大幅減少資料中心使用空間,並將每瓦效能提升好幾個數量級;其中,已量產的首款SoW產品採用以邏輯晶片爲主的整合型扇出(InFO)技術,而採用CoWoS技術的晶片堆疊版本,預計2027年準備就緒。

隨堆疊技術發展,AI晶片體積愈來愈大,未來一片晶圓可能切出低於十顆的超級晶片,封裝能量則成爲關鍵;法人指出,臺積電龍潭先進封裝2萬片月產能已滿,竹南AP6廠爲目前擴產主力,中科第四季陸續展開進機,加緊趕備量能。

臺積電系統整合晶片(SoIC)已成爲3D晶片堆疊的領先解決方案,其中,AMD爲SoIC首發客戶,MI300即以SoIC搭配CoWoS。蘋果也正式加入生成式AI戰局,業界指出,旗下第一顆3D封裝SoIC產品將是AI伺服器上ARM based CPU,代號爲M4 Plus 或M4 Ultra,最快將於明年下半年亮相,而此3D封裝SoIC技術將於2026年進一步下放至消費性MacBook M 系列處理器晶片。

輝達則於明年下半年推出沿用chiplet及CoWoS-L封裝架構的R100,2026年纔將正式推出採3D封裝方案之SoIC+CoWoS-L 的X100(暫定名)。